- v50 information can now be added to pages in the main namespace. v0.47 information can still be found in the DF2014 namespace. See here for more details on the new versioning policy.

- Use this page to report any issues related to the migration.

User:Green Sprite

Dwarftel Core d1[edit]

The Dwarftel Core d1 is a dwarven computer that uses primarily toggle-based mechanical logic. It is a simple processor that can add, subtract, binary shift, perform bitwise 'and' and 'not'. The processor also has 16 bytes of memory which it can write and read to. The program is kept on the memory.

Registers[edit]

| A | Main register, input of arithmetic operators and where the results are written. |

| B | Secondary register, most operations that need two inputs will use this register. |

| C | Conditional register, involved in low-level if statements. |

| PC | Program counter which keeps track of the memory address for the next instruction. |

Instructions[edit]

| 0x0 | Halt. |

| 0x1 | Load memory address to A. |

| 0x2 | Copy A to B. |

| 0x3 | Copy A to C. |

| 0x4 | Copy A to PC if C is not 0. |

| 0x5 | Store A to memory address. |

| 0x6 | \--- |

| 0x7 | \--- |

| 0x8 | Add A + B. Write result to A. |

| 0x9 | Increment 1 to A. |

| 0xA | Subtract A - B. Write result to A. |

| 0xB | Decrement 1 from A. |

| 0xC | Shift A left by given amount. |

| 0xD | Shift A right by given amount. |

| 0xE | Bitwise A and B. Write result to A. |

| 0xF | Bitwise not A. Write result to A. |

Memory Cell[edit]

Single bit cell[edit]

Design for single bit memory cell found here

Byte cell[edit]

Design for byte:

| O | ═ | ╦ | ╦ | ═ | ═ | ╦ | ╦ | ═ | ═ | ╦ | ╦ | ═ | ═ | ╦ | ╗ |

| ╥ | ☼ | ╚ | ╝ | ╥ | ☼ | ╚ | ╝ | ╥ | ☼ | ╚ | ╝ | ╥ | ☼ | ╚ | ╝ |

| ║ | O | ╥ | ☼ | ║ | O | ╥ | ☼ | ║ | O | ╥ | ☼ | ║ | O | ╥ | ☼ |

| ╨ | ☼ | ║ | O | ╨ | ☼ | ║ | O | ╨ | ☼ | ║ | O | ╨ | ☼ | ║ | O |

| ╔ | ╗ | ╨ | ☼ | ╔ | ╗ | ╨ | ☼ | ╔ | ╗ | ╨ | ☼ | ╔ | ╗ | ╨ | ☼ |

| ╚ | ╩ | ═ | ═ | ╩ | ╩ | ═ | ═ | ╩ | ╩ | ═ | ═ | ╩ | ╩ | ═ | O |

The byte cell is made up of eight individual single bit memory cells. The diagram shows only the track layer, the minecart and roller/furniture layers can be derived from the diagram above and the single bit design.

Memory write[edit]

Multiple byte cells are created close together to create the actual memory. A register for writing to memory, consisting of a byte cell is created. The pressure plate in each bit of the register connects to the ☼ northern gear and the ☼ sourthern gear assembly of the respective bit of all bytes in memory. The southern gear assembly is inverted. On a layer above, power is provided to all of the gears assemblies of each byte. A binary decoder selects a byte to activate in the layer above. Writing works by letting power flow first only to the byte being written to, and then the individual bits being turned on or off. To minimize the number of linkages in the reading of memory, the pressure plate being activated corresponds to a 0, and the pressure plate being lifted (unactivated) corresponds to a 1.

Memory read[edit]

The following diagram has multiple z-levels, click the diagram and press < or > to go up and down.

| ║ | ☼ | ☼ | ☼ | ☼ | ☼ | ☼ | ☼ | ☼ | ||||||||

| ☼ | ☼ | ═ | ☼ | ═ | ☼ | ═ | ☼ | ═ | ☼ | ═ | ☼ | ═ | ☼ | ═ | ☼ | |

| ║ | ||||||||||||||||

| ║ | ☼ | ☼ | ☼ | ☼ | ☼ | ☼ | ☼ | ☼ | ||||||||

| ☼ | ☼ | ═ | ☼ | ═ | ☼ | ═ | ☼ | ═ | ☼ | ═ | ☼ | ═ | ☼ | ═ | ☼ | |

| ║ | ||||||||||||||||

| ║ | ☼ | ☼ | ☼ | ☼ | ☼ | ☼ | ☼ | ☼ | ||||||||

| ☼ | ☼ | ═ | ☼ | ═ | ☼ | ═ | ☼ | ═ | ☼ | ═ | ☼ | ═ | ☼ | ═ | ☼ | |

| ║ | ||||||||||||||||

| ║ | ☼ | ☼ | ☼ | ☼ | ☼ | ☼ | ☼ | ☼ | ||||||||

| ☼ | ☼ | ═ | ☼ | ═ | ☼ | ═ | ☼ | ═ | ☼ | ═ | ☼ | ═ | ☼ | ═ | ☼ | |

| . | ||||||||||||||||

| . | Z | = | 1 | |||||||||||||

| . | ||||||||||||||||

| ║ | ☼ | ☼ | ☼ | ☼ | ☼ | ☼ | ☼ | ☼ | ||||||||

| ☼ | ☼ | ═ | ☼ | ═ | ☼ | ═ | ☼ | ═ | ☼ | ═ | ☼ | ═ | ☼ | ═ | ☼ |

| O | O | O | O | O | O | O | O | |||||||||

| ^ | ■ | ☼ | ^ | ■ | ☼ | ^ | ■ | ☼ | ^ | ■ | ☼ | |||||

| ╚ | ╝ | ║ | ╚ | ╝ | ║ | ╚ | ╝ | ║ | ╚ | ╝ | ║ | |||||

| ☼ | ☼ | ☼ | ☼ | ☼ | ☼ | ☼ | ☼ | |||||||||

| ║ | ║ | ║ | ║ | ║ | ║ | ║ | ||||||||||

| ║ | ║ | ║ | ║ | ║ | ║ | ║ | ||||||||||

| ☼ | ☼ | ☼ | ☼ | ☼ | ☼ | ☼ | ☼ | |||||||||

| ║ | ║ | ║ | ║ | ║ | ║ | ║ | ||||||||||

| ║ | ║ | ║ | ║ | ║ | ║ | ║ | ||||||||||

| ☼ | ☼ | ☼ | ☼ | ☼ | ☼ | ☼ | ☼ | |||||||||

| ║ | ║ | ║ | ║ | ║ | ║ | ║ | ||||||||||

| ║ | ║ | ║ | ║ | ║ | ║ | ║ | ||||||||||

| ☼ | ☼ | ☼ | ☼ | ☼ | ☼ | ☼ | ☼ | |||||||||

| ║ | ║ | ║ | ║ | ║ | ║ | ║ | ||||||||||

| . | ||||||||||||||||

| . | Z | = | 0 | |||||||||||||

| . | ||||||||||||||||

| ☼ | ☼ | ☼ | ☼ | ☼ | ☼ | ☼ | ☼ | |||||||||

| O | O | ║ | O | O | ║ | O | O | ║ | O | O | ║ | |||||

| ^ | ■ | ☼ | ^ | ■ | ☼ | ^ | ■ | ☼ | ^ | ■ | ☼ | |||||

| ╚ | ╝ | ╚ | ╝ | ╚ | ╝ | ╚ | ╝ |

In the design, each row of red gear assemblies ☼ are linked to the row of pressure plates in a byte. The purple gear assemblies ☼ are normally inverted and decide which byte to read. A binary decoder selects which purple gear assembly to engage. Reading works by first letting power flow through a single purple gear assembly corresponding to one byte and then through the red gear assemblies that are engaged. The lower z level (0) carries the power to a power to signal converter (pts converter).

Binary Decoder[edit]

I will be using Jong's design for a binary decoder. Binary decoders allow for memory addressing and selecting operations from an opcode.

Adder[edit]

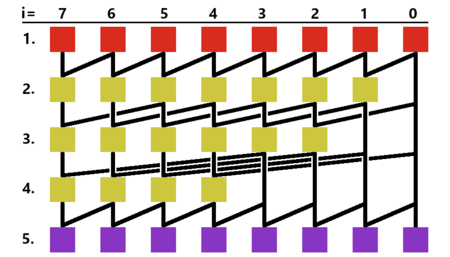

The adder used in the Dwarftel Core d1 is a kogge-stone adder, which is a type of carry-lookahead adder. It consists of 3 components chained in a certain way.

Components:

| O | ═ | ═ | ═ | ═ | ═ | ═ | ═ | ═ | ═ | ═ | ═ | ═ | ═ | ═ | ═ | ═ | ═ | ═ | O |

| ^ | ■ | ☼ | ☼ | A | n | d | g | a | t | e | |||||||||

| ╚ | ╝ | ||||||||||||||||||

| O | ═ | ═ | ═ | ═ | ═ | ═ | ═ | ═ | ═ | ═ | ═ | ═ | ═ | ═ | ═ | ═ | ═ | ═ | O |

| ^ | ■ | ☼ | X | o | r | g | a | t | e | ||||||||||

| ╚ | ╝ | ||||||||||||||||||

| O | ═ | ═ | ═ | ═ | ═ | ═ | ═ | ═ | ═ | ═ | ═ | ═ | ═ | ═ | ═ | ═ | ═ | ═ | O |

| O | O | ☼ | ☼ | ☼ | ( | x | a | n | d | y | ) | o | r | z | |||||

| ^ | ■ | ☼ | ☼ | ☼ | |||||||||||||||

| ╚ | ╝ |

In the and gate, power is fed to the rightmost gear assembly. Both gear assemblies are inverted. Each gear assembly is linked to one input, power goes into the pts converter only when both inputs are open.

In the xor gate, power is fed to the gear assembly. The gear assembly is inverted and linked to both inputs. When either input, but not both, are open, power goes to the pts converter.

In the last component, there are three non-commutative inputs. Power is fed to the green gear assembly ☼. Input z is linked to the red gear assembly ☼. Inputs x and y are linked to either blue gear assembly ☼, creating an and gate. Both blue gears and the reg gear are inverted.

The adder takes the following steps:

- G0i = Ai and Bi. P0i = Ai xor Bi (both for 0 ≤ i < 8)

- G1i = (P0i and G0(i-1)) or G0i. P1i = P0i and P0(i-1) (both for 1 ≤ i < 8)

- G2i = (P1i and G1(i-2)) or G1i. P2i = P1i and P1(i-2) (both for 2 ≤ i < 8)

- G3i = (P2i and G2(i-4)) or G2i. P3i = P2i and P2(i-4) (both for 4 ≤ i < 8)

- Si = P(last)i xor G(last)(i-1)

Where i is the bit index on the byte (0 being the least significant bit and 7 being the most significant bit). A and B are the registers used as inputs. P(last)i is the latest iteration of Pi. For example, P(last)1 is P1,1, since steps 3 and 4 don't apply to i=1. Similarly, G(last)i is the latest iteration of Gi.

The only delays are caused by pressure plates which turn off 99 ticks after a minecart stops pressing it. Just to be safe (and because minecarts might require some travel time) I will assume 103 ticks of delay per step. Since there's 5 steps in the process, there's a total of 515 ticks

Edge Detectors (Rising and Falling)[edit]

Rising edge detector design:

| ╔ | ╢ | ┼ | ╢ | ┼ | ^ | ╗ |

| ╚ | ═ | ═ | ═ | ═ | ═ | ╝ |

The rising edge detector sends a pulse when an open signal is sent. Both rollers ╢ are always active and sending the cart from west to east. The red door ┼ is linked to the input. The input is also connected to a not gate, which feeds to a pts converter. The pts converter connects to the red door ┼. The pressure plate ^ is the output. A minecart is placed on the roller between both doors. When the input sends a open signal the green door opens, letting the minecart past the pressure plate. The pressure plate sends a pulse starting instantly for 99 ticks. At the same time, the red door closes, stopping the minecart from going through. When the input sends a closed signal again, the red door opens, but the green door closes, so the minecart is set back to the original position.

The falling edge detector is the same as the rising edge detector, but the green and red doors are flipped.