- v50 information can now be added to pages in the main namespace. v0.47 information can still be found in the DF2014 namespace. See here for more details on the new versioning policy.

- Use this page to report any issues related to the migration.

Difference between revisions of "Memory (computing)"

m (Creating page for DF2014 (131/279)) |

m |

||

| (7 intermediate revisions by 3 users not shown) | |||

| Line 1: | Line 1: | ||

| − | {{ | + | {{migrated article}} |

| − | {{Quality| | + | {{Quality|Unrated}} |

{{Computing}} | {{Computing}} | ||

{{av}} | {{av}} | ||

| − | Memory is used for storing values and states in dwarven [[computing]]. Typically, binary memory is used, but this isn't strictly necessary. There are multiple ways to set up a memory cell, depending on whether one is using [[mechanical logic|mechanical]], [[fluid logic|fluid]], [[creature logic]], or [[minecart logic]]. With binary memory, each cell has two possible states, generally referred to as 0 and 1, or true and false. | + | '''Memory''' is used for storing values and states in dwarven [[computing]]. Typically, binary memory is used, but this isn't strictly necessary. There are multiple ways to set up a memory cell, depending on whether one is using [[mechanical logic|mechanical]], [[fluid logic|fluid]], [[creature logic|creature]], or [[minecart logic]]. With binary memory, each cell has two possible states, generally referred to as 0 and 1, or true and false. |

===Flip-flops versus latches=== | ===Flip-flops versus latches=== | ||

| − | The most basic characteristic of memory in Dwarf Fortress is that it acts as a signal splitter: given a series of on-off signal cycles, it outputs a series of alternating on or off signals. Memory that does this, and only this, acts like a flip-flop: every time you trigger the memory, it changes state. Such memory is perfect for devices such as [[Adder (Computing)|counters]]. However, it's common to desire the ability to write state directly to your memory, rather than toggling it-- that is, to write either '''true''' or '''false''' to memory directly, without knowing the current state of the memory. This can be described with a chart where the memory value feeds back into itself: | + | The most basic characteristic of memory in ''Dwarf Fortress'' is that it acts as a signal splitter: given a series of on-off signal cycles, it outputs a series of alternating on or off signals. Memory that does this, and only this, acts like a flip-flop: every time you trigger the memory, it changes state. Such memory is perfect for devices such as [[Adder (Computing)|counters]]. However, it's common to desire the ability to write state directly to your memory, rather than toggling it-- that is, to write either '''true''' or '''false''' to memory directly, without knowing the current state of the memory. This can be described with a chart where the memory value feeds back into itself: |

{| class="wikitable" border=1 | {| class="wikitable" border=1 | ||

|- | |- | ||

| Line 36: | Line 36: | ||

|}<br /> | |}<br /> | ||

===Performance=== | ===Performance=== | ||

| − | Memory systems in | + | Memory systems in a fortress, thankfully, are very good at maintaining their value (in the absence of any [[troll]]s), but they are still plagued by problems with latency and long refractory periods. Latency refers to the length of time before which a change in value will register, and the refractory period refers to the period after writing to memory during which one cannot reliably write to it a second time. Because of the delays involved with [[pressure plate]]s, latency and refractory period for a given memory cell often depend on which state the memory is being changed to. For instance, the mechanical hybrid cell below has nearly no latency when being written as true, but around 100 ticks of latency when being written as false. |

Some designs can trade simplicity or material needs for costs in performance. | Some designs can trade simplicity or material needs for costs in performance. | ||

| Line 131: | Line 131: | ||

{{Category|Computing}} | {{Category|Computing}} | ||

| + | [[ru:Memory (computing)]] | ||

Latest revision as of 14:28, 26 October 2025

| This article was migrated from DF2014:Memory (computing) and may be inaccurate for the current version of DF (v53.11). See this page for more information. |

| Part of a series on |

| Computing |

|---|

| Logic: Animal • Creature • Fluid • Mechanical • Minecart |

| Components: Adder • Memory • Repeater |

v53.11 · v0.47.05 This article is about the current version of DF.Note that some content may still need to be updated. |

Memory is used for storing values and states in dwarven computing. Typically, binary memory is used, but this isn't strictly necessary. There are multiple ways to set up a memory cell, depending on whether one is using mechanical, fluid, creature, or minecart logic. With binary memory, each cell has two possible states, generally referred to as 0 and 1, or true and false.

Flip-flops versus latches[edit]

The most basic characteristic of memory in Dwarf Fortress is that it acts as a signal splitter: given a series of on-off signal cycles, it outputs a series of alternating on or off signals. Memory that does this, and only this, acts like a flip-flop: every time you trigger the memory, it changes state. Such memory is perfect for devices such as counters. However, it's common to desire the ability to write state directly to your memory, rather than toggling it-- that is, to write either true or false to memory directly, without knowing the current state of the memory. This can be described with a chart where the memory value feeds back into itself:

| input | latch state | output | new latch state |

|---|---|---|---|

| 0 | 0 | none | 0 |

| 0 | 1 | off | 0 |

| 1 | 0 | on | 1 |

| 1 | 1 | none | 1 |

Performance[edit]

Memory systems in a fortress, thankfully, are very good at maintaining their value (in the absence of any trolls), but they are still plagued by problems with latency and long refractory periods. Latency refers to the length of time before which a change in value will register, and the refractory period refers to the period after writing to memory during which one cannot reliably write to it a second time. Because of the delays involved with pressure plates, latency and refractory period for a given memory cell often depend on which state the memory is being changed to. For instance, the mechanical hybrid cell below has nearly no latency when being written as true, but around 100 ticks of latency when being written as false.

Some designs can trade simplicity or material needs for costs in performance.

Fluid Logic[edit]

Simple fluid logic latches rely on an infinite source and infinite drain, storing information in the form of the presence or absence of water in a particular location.

| ═ | ═ | ═ | ═ | ═ |

| ~ | X | ^ | X | ~ |

| ═ | ═ | ═ | ═ | ═ |

In this design, water flows from an infinite source ~ over an output pressure plate ^ toward an infinite drain ~. Its flow is controlled by two floodgates, X, and X, linked to two separate inputs. When X is open and X closed , water will cover ^ and remains so, regardless of the state of X.

If X is opened while X is closed, water will leave ^ and the tile will remain empty of water until X opens again.

This design has relatively high latency, because of the 100 tick delay associated with floodgates. Replacing the floodgates with doors, which have no reaction delay, greatly accelerates the response of the latch, but the overall performance is still limited by the reset period of pressure plates. Given careful enough design and sufficient water pressure, the latency of a write to true can approach 10, with the latency of a write to false around 110.

Creature Logic[edit]

| ╔ | ═ | ╗ | |||||

| ═ | ═ | ═ | ╝ | ┼ | ╚ | ═ | ═ |

| p | ¢ | ^ | ¢ | ¢ | ^ | ¢ | p |

| ═ | ═ | ╗ | ┼ | ╔ | ═ | ═ | ═ |

| ╚ | ═ | ╝ |

In this circuit, a creature placed between in the middle seeks its pathing goal p but is constrained by the hatches ¢ and ¢, each linked to the pressure plate ^ of the same color. When the door + is opened, the creature can move to the left (false) ^, and when the door + is opened, the creature can move to the right (true) ^, thus outputting to anything linked to that pressure plate. This is an example of memory for which it is possible to write a particular state, rather than just toggling, which allows for simpler design for some applications. Note also that rather than writing on a single on or off signal, it depends on an on-off cycle.

This design has good latency for creature logic systems, resulting in on signals around 40 ticks after writes and off signals around 150 ticks after writes. It has a 110 tick refractory period, representing the time necessary for the hatch covers to close.

Mechanical Logic[edit]

A gear assembly can function all on its own as a memory cell, being either active or disengaged. However, some complicated applications suggest the use of hybrid mechanical-fluid memory.

| z | + | 2 | |||

| ╔ | ═ | ☼ | ╔ | ═ | ╗ |

| ║ | % | % | ║ | ||

| ╚ | ═ | ╝ | ╚ | ═ | ╝ |

| z | + | 1 | |||

| ╔ | ═ | ☼ | ╔ | ═ | ╗ |

| ║ | % | % | ^ | ║ | |

| ╚ | ═ | ╝ | ╚ | ═ | ╝ |

| z | + | 0 |

| ╔ | ═ | ╗ |

| ║ | ~ | ║ |

| ╚ | ═ | ╝ |

In this design, two separately powered pump stacks, %% and %%, are placed over each other-- the lower one, pumping to the right, and the higher one pumping to the left. When the water ~ is lying in the rightmost (true) cell, it activates a pressure plate ^. To write true to the memory, one triggers the lower gear assembly ☼, activating the lower pump, and to write false, one activates the higher gear assembly ☼ and pump stack. Like the creature logic memory above, this cell can be written as specifically true or false, and depends on an on-off cycle as input.

This design has very good latency (from almost nothing for a write as true to 100 ticks for a write as false) and no real refractory period-- it can be written to immediately following a previous write, although it does depend on the completion of the previous write signal (receiving the off component of the signal) before writing again.

Memory versus Power-to-signal[edit]

It can be tricky to differentiate memory from power to signal conversion. Through feedback, power-to-signal devices can often be changed into memory cells, and powered memory devices can be adapted into power-to-signal. Previous to the introduction of minecarts, the most common power-to-signal device bore strong resemblance to the memory cell described above. There is, however, a large difference between memory and power-to-signal. While memory designs receive on-off signal cycles and output discrete on or off signals in return, power-to-signal converters translate one type of binary information (power on/off) into another (signal on/off). That is, a signalling device that receives then loses power should return a full on-off signal cycle.

Minecart Logic[edit]

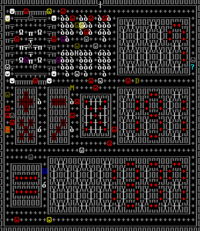

There are numerous ways for minecarts to hold information. Some memory designs use movement or the absence of movement; others use just the position of a minecart. Advanced designs could use the weight or direction of movement of a minecart. The following powered minecart design by Bloodbeard is the smallest memory circuit currently known to dwarvenkind:

| K | e | y | : | ||||||||||||||||||||

| O | O | W | a | l | l | ||||||||||||||||||

| ■ | ☼ | ■ | C | o | p | p | e | r | m | i | n | e | c | a | r | t | |||||||

| ■ | ■ | I | r | o | n | m | i | n | e | c | a | r | t | ||||||||||

| ╧ | ☼ | ☼ | ☼ | G | e | a | r | s | |||||||||||||||

| O | ╧ | R | o | l | l | e | r | s | |||||||||||||||

| ^ | P | r | e | s | s | u | r | e | p | l | a | t | e | ||||||||||

| O | ║ | M | i | n | e | c | a | r | t | t | r | a | c | k | s | ||||||||

| ╧ | ☼ | ╥ | ╨ | T | r | a | c | k | e | n | d | s | |||||||||||

| ^ | |||||||||||||||||||||||

| ╧ | ☼ | ||||||||||||||||||||||

| O | |||||||||||||||||||||||

| O | |||||||||||||||||||||||

| ╥ | ☼ | ||||||||||||||||||||||

| ║ | |||||||||||||||||||||||

| ╨ | ☼ | ||||||||||||||||||||||

| O | |||||||||||||||||||||||

The diagram shows the minecart layer at the top, the roller/furniture layer in the middle, and finally the track layer at the bottom. When the northern gear assembly is activated, powering the northern roller, a heavy minecart (copper, in this example) is pushed southwards. This pushes a lighter minecart (iron here) south, and triggers a pressure plate that is built to only signal on the weight of a copper minecart, and not on the weight of the lighter iron minecart. With the activation of the southern gear assembly, the situation reverses. The iron minecart pushes on to the pressure plate, and an off signal is sent.

Memory addressing[edit]

In complicated designs, one may wish to use a memory cell abstractly-- to represent any number of different values. To use multiple such abstract cells, it's necessary to specify exactly which memory cell one wishes to read from or write to at any given moment.

This is simplest in mechanical logic. A grid of gear assemblies can represent rows and columns, and by disengaging control gears for all but the cell that lies at that particular row/column intersection, one can easily refer to a specific cell. Strict fluid logic can do something similar, by controlling the input of water to memory cells, although this involves long delays. With the creature logic design, one can use additional doors to restrict writes to any cells not referenced.

Alternate design[edit]

Because most memory is used for a specific application, there is no single best design. It is not uncommon to see functionality built into memory circuits-- a simple circuit that increments contains its own memory. Alternate designs are important when memory needs to be written to in various ways (toggle versus specific value) or when latency and refractory period are unimportant compared to resource requirements such as space.